25RIA120

? Improved glass passivation for high reliability

and exceptional stability at high temperature

? High dI/dt and dV/dt capabilities

? Standard package

? Low thermal resistance

? Metric threads version available

? Types up to 1200 V VDRM/VRRM

? Designed and qualified for industrial and consumer level

3296Y-1-502LF

74F74N

These devices contain two independent positiveedge-triggered D-type flip-flops. A low level at the

preset (PRE) or clear (CLR) inputs sets or resets

the outputs regardless of the levels of the other

inputs. When PRE and CLR are inactive (high),

data at the data (D) input meeting the setup time

requirements is transferred to the outputs on the

positive-going edge of the clock pulse. Clock

triggering occurs at a voltage level and is not

directly related to the rise time of the clock pulse.

Following the hold-time interval, data at the

D input may be changed without affecting the

levels at the outputs.

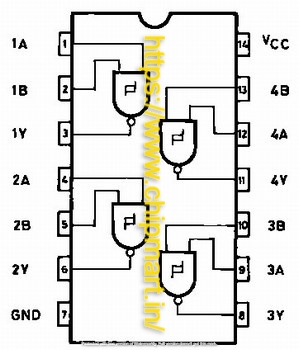

74HC132

Features

? Buffering of inputs

? Wide working temperature range: -40?C to 85?C

?Fanout up to 10 LSTTL loads

? Significant power savings over LSTTL logic ICs

Application

- Used to make alarm/tamper detect circuit

- S-R latch